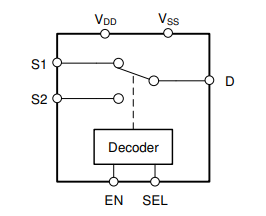

TMUX7219-Q1 is a complementary metal oxide semiconductor (CMOS) switch with latching immunity. The device in a single channel, 2:1 (SPDT) configuration operates in a single power supply (4.5 V to 44 V), a dual power supply (± 4.5 V to ± 22 V), or an asymmetric power supply (such as VDD=12v, VSS=- 5v). It supports bidirectional analog and digital signal source (Sx) and drain (D) pins ranging from VSS to VDD. TMUX7219-Q1 can enable or disable the control EN pin in the following ways.

Block Diagram

When disabled, both signal that the path switch is closed. When enabled, SEL pin can be used to open signal path 1 (S1 to D) or signal path 2 (S2 to D). All logic control inputs support logic level from 1.8 V to VDD to ensure TTL and CMOS logic compatibility during operation. The fail safe logic circuit allows the voltage supply pin on the control pin to protect the equipment from potential influence and damage.

The MUX72xx family provides latching immunity to prevent unwanted parasitic structures between high current events that often cause over-voltage events in the device. The typical latch state continues until the power supply track is turned off and may cause equipment failure. The blocking exemption feature allows TMUX72xx series switches and multiplexers to be used in harsh environments.

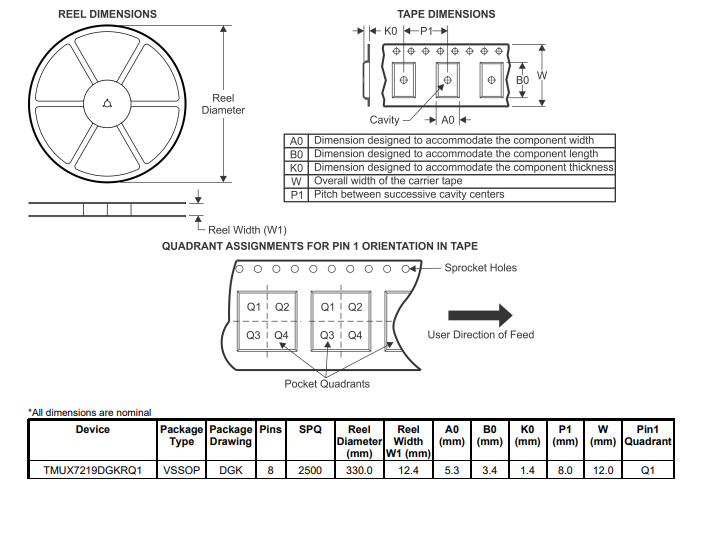

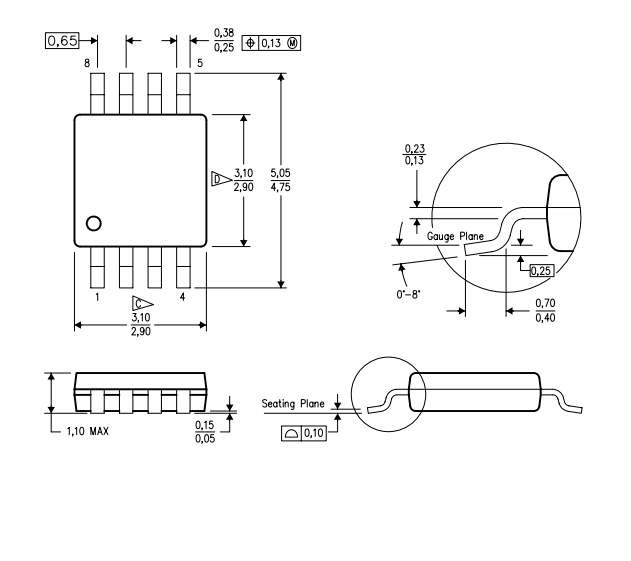

Packaging Material Information